### **International Journal of Engineering Research and Development**

e-ISSN: 2278-067X, p-ISSN: 2278-800X, www.ijerd.com

Volume 13, Issue 1 (January 2017), PP.56-61

# Carbon Nanotube Based Circuit Designing: A Review

Neelofer Afzal<sup>1</sup>,

<sup>1</sup>Department of Electronics And Communication Engineering, Jamia Millia Islamia, New Delhi.

**ABSTRACT:-** A new material and its associated device which have potential to replace Si and CMOS and can extend the scalability of devices below 22 nm is the carbon nanotube (CNT) and its associated transistor, the carbon nanotube field effect transistor (CNTFET). CNT possesses unique properties that make it a promising future material. Similarly, CNTFET is a promising basic building block to complement the existing silicon based MOSFET and can result in the extension of the validity of Moore's law further. This paper presents the state of the art literature related to carbon nanotubes, carbon nanotube field effect transistors and CNTFET based circuit designing. A review of CNTFET based analog and digital circuits has been presented. It has been observed that the use of CNTFET can improve the performance of both analog and digital circuits. The work will be of utmost use to the people working in the field of CNT based analog and digital circuit designing.

**Keywords:-** Carbon Nanotubes (CNT), CNT field effect transistor (CNTFET), analog designing, digital designing, operational amplifier.

#### I. INTRODUCTION

Conventional bulk technology have been a back bone for circuit designing for the last three four decades. This can be attributed to scaling of physical dimensions of MOS devices, which has resulted in significant performance enhancement of MOSFETs[1-3]. However, further scaling of devices below 22nm face severe challenges in terms of short channel effects, leakage, loss of control, reliability issues, excessive process variations, self-heating etc. These issues pose dramatic challenges to circuit designing and fabrication at nanoscale [4-7]. Thus, there is an urgent need for alternative material to silicon and alternative device structure to bulk MOSFET, so that the performance degradation of devices below 22 nm technology node can be stopped. New device structures like double gate MOSFETs, FinFETs, Trigate devices, gate around devices, strained silicon devices, and high-k metal gate devices have been developed. These alternatives have indeed improved the performance and have resulted in scaling the device dimensions below 22 nm, however, the structures of these novels devices are complex, costly and have thermal issues [3-6]. Carbon nanotube (CNT) and CNTFET are a new material and its associated device which have potential to replace Si and CMOS circuitry and can extend the scalability of devices below 22 nm. CNT possesses unique properties that make it a promising future material. Similarly, CNTFET is a promising basic building block to complement the existing silicon based MOSFET and can result in the extension of the validity of Moore's law further. These advantages of CNTFETs will be reflected in high speed, low power, thermally efficient, highly dense CNTFET based integrated circuits. The use of CNTFETs in designing and developing analog and digital circuits will significant address the issue of high power consumption, large delay, self-heating, leakage power and other reliability related issues of the state of the art electronics circuitry. These advantages of CNTFETs have motivated the researchers to design and simulated CNTFET based electronic circuitry. Since a lot of work has been done in the CNTFET based digital designing domain, the CNTFET based analog designing is comparatively an unexplored area. This work will provide the review of the CNT based analog and digital circuit designing [6-20]

The paper is divided into five sections. Section II discusses the details about carbon nanotube and CNTFET. Section III gives us the review of CNT based digital designing, Sectional IV gives us the review of CNT based analog designing and section V concludes the paper.

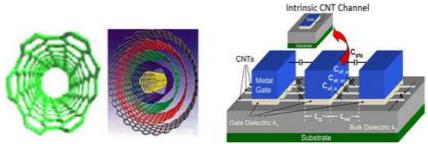

## II. CARBON NANOTUBE FIELD EFFECT TRANSISTOR

Carbon nanotubes (CNT), an allotrope of carbon, were first discovered by Dr. Sumio Iijima of NEC Japan in 1991, while studying the surface of graphite electrode in an electric arc discharge [6]. They possess unique and extra ordinary mechanical, electrical and thermal properties and are considered as promising future materials. They are 100 times stronger than steel, have superior field emission property, have very large current density of more than  $10^9$  A/cm², and have thermal conductivity more than that of diamond [7-20]. They exist in two forms: (i) Single wall carbon nanotube (SWCNT) and (ii) multiwall carbon nanotube and can have metallic and semiconducting properties, as shown in Fig. 1. A unique property of CNTs is their ability to show metallic and semiconducting behavior. It all depends on the chirality or chirality vector (*C*h) of CNT that determines whether a CNT is metallic or semiconducting. A CNT shows metallic characteristics if n = m or n - m = 3i where i is an integer, otherwise it is a semiconductor [12-20]. An important and prominent application of a CNT is

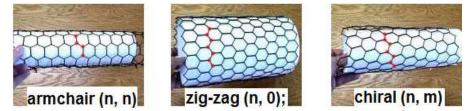

Carbon-nanotube field effect transistor (CNTFET). A CNTFET is a promising future device and has a potential to replace the conventional MOSFET and the extend the validity of Moore's law further. A CNTFET has large transconductance, very low intrinsic capacitance, nearly ideal subthreshold slope and very strong covalent bonding [10-18]. It has been found that the CV/I characteristics of an intrinsic *n* or *p* type CNTFET is 13 times better than the conventional bulk MOSFET. There are two types of CNTFETs: Schottky Barrier (SB) CNTFET (SB-CNTFET) and MOSFET-like CNTFET (MOS-CNTFET). A Schottky barrier type CNTFET can be realized by directly attaching the intrinsic single wall CNTs to the metal source/drain contacts. This type of CNTFET shows ambipolar carrier transport. The MOSFET like CNTFET has CNT based channel connecting heavily doped source and drain regions. It has unipolar conduction, has large ON current (I<sub>ON</sub>), higher I<sub>ON</sub>/I<sub>OFF</sub> ratio and lower leakage power. It shows better scalability in comparison to the SB-CNTFET [8-15]. CNTs can exist in three forms, armchair zig-zag and chiral, as shown in Fig. 2.

Fig. 1: (a) Single wall CNT (b) multi wall CNT (c) 3D CNFET structure [5-6].

Fig. 2. Three types of SWCNTs based on the chiral vector and chiral angle ( $\theta$ )[5-6, 19-20]

#### III. CNFET BASED CIRCUIT DESIGNING

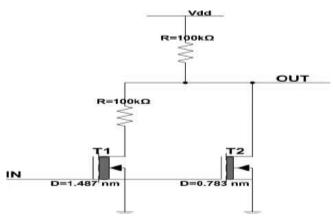

The researchers have initially started utilizing CNTs in digital designing to improve the performance of digital circuits. The various digital blocks, like gates, flip-flops, decoders, encoders, counters memory, adders etc have been designed and simulated using CNTFETs. Sheng Lin et al. [7] have designed CNTFET based ternary logic gates, as shown in Fig. 3. The ternary logic gates are promising alternatives to the conventional logic gates and result in power efficient and compact designing. The simulation study using SPICE has revealed that the proposed ternary logic consumes less power and results in small delay in comparison the conventional technology.

Fig. 3: Schematic diagram of CNTFET-based standard ternary inverter (STI) [7].

M. Bagherizadeh et. al. [8] have designed and simulated novel, low-power and high-speed dynamic full-adder cells using CNTFET, as shown in Fig. 4. It has been observed that the proposed adders consume less power and result in less delay in comparison the conventional technology based adders.

Fig. 4: The proposed CNTFET based low power dynamic full adder [8].

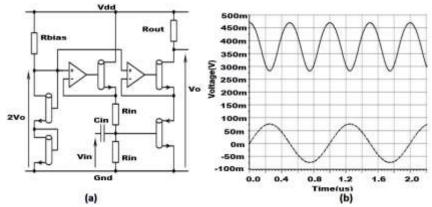

Fabien Pregaldiny et al.[9] have designed an analog frequency doubler circuit employing both unipolar and ambipolar CNTFETs, , as shown in Fig. 5. Such a frequency doubler circuit uses the symmetry of the CNTFET ambipolar response. The frequency of the output signal in a frequency doubler is twice the frequency of the input signal, as expected [90].

Fig. 5. (a) CNT based Frequency doubler (b) Response of the proposed frequency doubler [9]

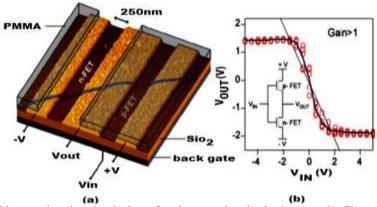

V. Derycke, R. et al. [10] have experimentally shown that the n-type CNTFETs cannot be realized by doping only; however, a simple annealing of SWNT-based p-FETs in a vacuum will create the n-type CNTFETs. They have used their technique to build first CNT based logic gates, voltage inverters. They have employed spatially resolved doping to implement logic function on a single CNT bundle, , as shown in Fig. 6

**Fig. 6.** (a) AFM image showing the design of an intra-molecular logic gate. (b) Characteristics of the resulting intra-molecular voltage inverter [10].

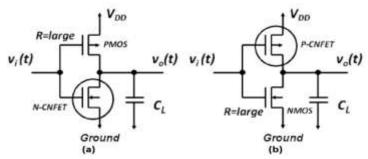

Fahad Ali Usmani and Mohammad Hasan [11-12] have used CNTFETs for designing analog signal processing circuitry, as shown in Fig. 7. They have for the first time, performed the performance and reliability analysis of pure and hybrid CMOS–CNFET technologies based analog amplifier.

Fig.7. Hybrid technology Inverting Amplifier (a) PMOS-NCNTFET (b) PCNTFET-NMOS [11-12].

Ale Imran et al. [13] have designed and simulated a high performance CNTFET based second generation current conveyor (CCII±) at 32-nm technology node, , as shown in Fig. 8. F. A. Usmani et. al. [12] proposed a CNTFET based Class AB OP-AMP. They compared the performance of the proposed CNTFET based OP-AMP with the Strained Silicon and conventional CMOS based OP-AMP at 32nm using HSPICE..

Fig. 8 CMOS op amp with Class AB output stage [13].

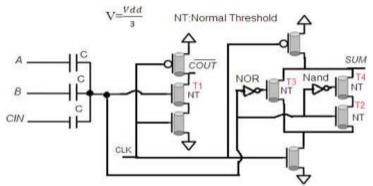

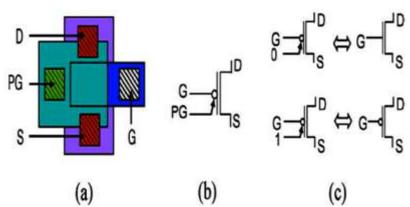

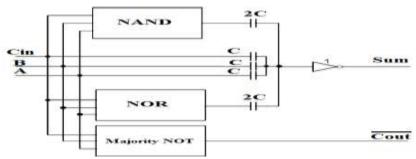

M. Haykel et.al.[14] have proposed flexible logic gate library for Ambipolar Logic designs using CNTFETS, as shown in Fig. 9. They realized generalized NOR-NAND-AOI-OAI primitives to implement XOR based functions using CNTFETs. Further, various blocks like multipliers, linear circuits, adders are designed using CNTFETs. They have observed a significant reduction in component requirement, reduced power delay and energy-delay-products in their designs. K. Navi et. al. [15] have proposed CNTFET based adder circuit using Inverter and three capacitors. This adder has a simple design, because it only uses capacitors and inverter in its structure. It has been observed that the delay and power-delay products are improved in the proposed structure. The circuit is simulated using HSPICE Software. K. Navi et.al [16] have designed and simulated CNTFET based full adder cell by varying supply, capacitive load and frequency at 32nm technology node, , as shown in Fig. 10. The simulation is carried out using HSPICE Simulator at supply voltages of 0.5V and 0.65V, with the operating frequencies of 250MHz and 500MHz. It has been observed that the proposed design has better speed and Power-Delay-Product in comparison to its CMOS counterpart.

Fig. 9: Double gate ambipolar transistor. (a) Layout. (b) Symbol. (c) Configuration as n-type and p-type [14].

Fig. 10 Schematic of proposed adder [15].

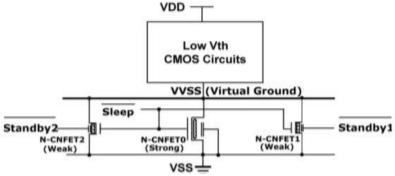

Fig. 11. Block diagram of the proposed multimode PG [16].

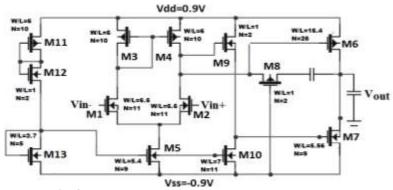

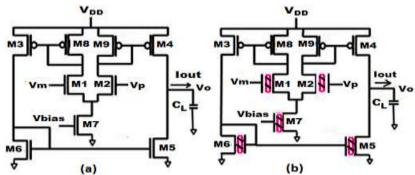

K. K. Kim et.al. [17] have a new proposed power gating techniques using hybrid technology i.e. both conventional MOS and CNTFET at 0.4V, , as shown in Fig. 11. It has been found that the proposed device leakage power, rush current and delay are reduced by 69.07%, 5.13% and 5.96% respectively in comparison to its CMOS based PG counterpart at 32nm technology node. N. Nizammudin et. al [18-20] has designed various CNTFET based analog blocks. He has design CNT based operational transconductance amplifiers. It has been observed that a significant improvement is achieved in those CNT based OTAs, , as shown in Fig. 12.

**Fig. 12.** Different topologies of OTAs designed and simulated (a) Conventional CMOS OTA (b) NCNTFET-PMOS-OTA [17-20].

## IV. CONCLUSIONS

Carbon nanotube is a wonderful material with some extra ordinary and unique properties. An important application of the CNT is the carbon nanotube field effect transistor. The presence of 1-D ballistic transport of charge carriers has resulted in a high mobility and large drive current (3-4 times higher than the bulk MOSFET) in a CNTFET. A CNTFET possesses large transconductance, low intrinsic capacitance, near ideal subthreshold slope and strong covalent bonding. In this paper, we presented the review of CNTFET based analog and digital circuit designing.

It has been found that the use of CNTFETs has improved the performance of all the circuits. The power consumption has significantly got reduced in these circuits. A lot of work has been done in the digital domain, however, a lot more can be done in the analog sector.

#### **REFERENCES**

- [1]. T. H. Ning, "Why BiCMOS and SOI BiCMOS," IBM Journal of Res and Dev., Vol. 46, No. 2/3, pp. 181-86, March 2002.

- [2]. A. Matsuzawa, "RF-SoC Expectations and required conditions," IEEE Transactions on Microwave Theory Technology, Vol.50, No. 1, pp. 245-253, Jan. 2002.

- [3]. G. McFarland and M. Flynn "Limits of scaling MOSFETs," Technical report CSLTr- 95-662, Jan. 1995

- [4]. Sajad A. Loan, S. Qureshi and S. S. K Iyer, "A New Partial Ground Plane Based MOSFET on Selective Buried oxide, A 2D simulation study" (IEEE Transactions on Electron Device, Vol. 57, No. 3, pp.671-680, March 2010).

- [5]. Sajad A. Loan, S. Qureshi and S. S. K Iyer, "A novel high breakdown lateral BJT on SOI with Multizone doped and multistep oxide" A numerical simulation study" Semiconductor Science and Technology Vol.24, No. 2, 2009.

- [6]. Sumio Iijima," Helical microtubules of graphitic carbon", Nature, Vol 354, 7th November, 1991

- [7]. Sheng Lin, Yong-Bin Kim, and Fabrizio Lombardi, ," CNTFET-Based Design of Ternary Logic Gates and Arithmetic Circuits", IEEE Transactions on Nanotechnology, Vol. 10, No. 2, March 2011

- [8]. M. Bagherizadeh and Mohammad Eshghi," Two novel low-power and high-speed dynamic carbon nanotube full-adder cells", Springer Open Journal, Nanoscale Research Letters 2011.

- [9]. Fabien Pregaldiny, Jean-Baptiste Kammerer et al., "Compact Modeling and Applications of CNTFETs for Analog and Digital Circuit Design", InESS/ENSPS, Parc d'innovation, BP 10413, 67412, France, IEEE Conference, 2006.

- [10]. Derycke, V.; Martel, R.; Appenzeller, J.; Avouris, "Carbon nanotube Inter and Inter molecular logic gates" Ph. Nano Lett. 2001, 1, 453.

- [11]. Usmani F A, Hasan M, 2010, Carbon nanotube field effect transistors for high performance analog applications: An optimum design approach ",Microelectronics Journal, 41, pp. 395–40.

- [12]. Fahad Ali Usmani and Mohd. Hasan, "Novel Hybrid CMOS and CNFET Inverting Amplifier Design for Area, Power and Performance Optimization", 2nd IEEE International Workshop on Electron Devices and Semiconductor Technology, 2009.

- [13]. Ale Imran et.al. "Optimized Design of Hybrid CMOS and CNFET 32 nm Dual-X Current Conveyor",2011 International Conference on Multimedia, Signal Processing and Communication Technologies.

- [14]. M. Haykel Ben-Jamaa et. al., "An Efficient Gate Library for Ambipolar CNTFET Logic", IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems", Vol. 30, No. 2, February 2011

- [15]. K. Navi et. al., "High Speed Capacitor-Inverter Based Carbon Nanotube Full Adder", Nanoscale Res Lett 5:859–862, 2010.

- [16]. Keivan Navi et.al. , "A low-voltage and energy-efficient full adder cell based on carbon nanotube technology", Nano-Micro Letters Vol. 2, No. 2 114-120 , 2010.

- [17]. Kyung Ki Kim et.al., "Hybrid CMOS and CNFET Power Gating in Ultralow Voltage Design", IEEE Transactions on Nanotechnology, Vol. 10, No. 6, November 2011.

- [18]. M, Nizamuddin Sajad A. Loan, Shuja A Abbasi and A. R. M. Alamoud, "Design and Comparative Analysis of High Performance cascode Carbon Nanotube based Operational Transconductance Amplifiers" IOP Nanotechnology, vol. 9, 2015(SCI Listed; IF=3.82).

- [19]. Sajad A. Loan, M, Nizamuddin, Shuja A Abbasi and A. R. M. Alamoud, "Design and Comparative Analysis of High Performance Carbon Nanotube based Operational Transconductance Amplifiers" World Scientific journal Nano, vol. 3, 2015(SCI Listed; IF=1.09).

- [20]. M. Nizamuddin, Sajad A. Loan, Shuja A. Abbasi and Abdul Rahman M Alamoud, Design and Simulation of High Performance Carbon Nanotube based Three Stage Operational Amplifiers, Elsevier's Material Today proceedings, AFM 2015

- [21]. M. Nizamuddin, PhD thesis, Design and simulation of CNT based devices for Nanoelectronics Applications, submitted to JMI New Delhi.